Vhdl Binary To Integer Converter

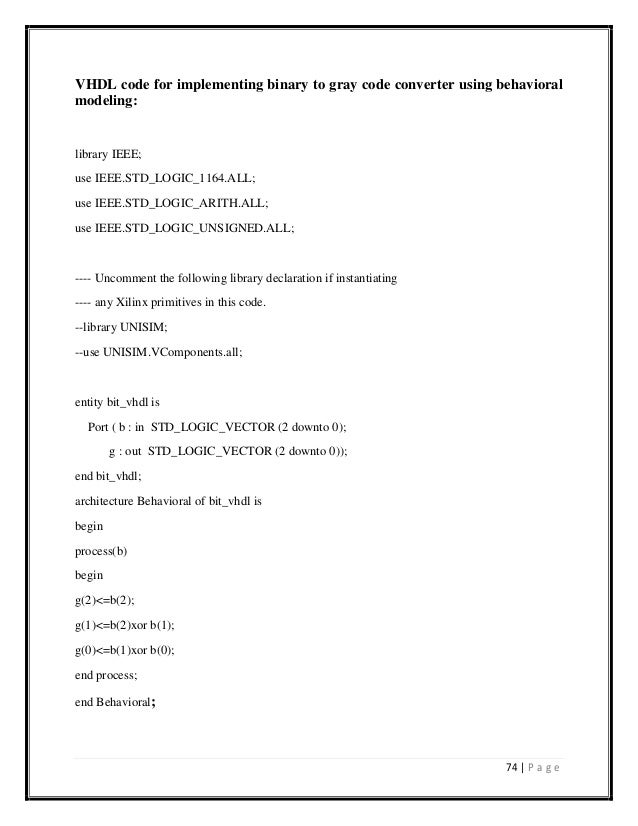

As others said, use ieee.numeric_std, never ieee.std_logic_unsigned, which is not really an IEEE package. However, if you are using tools with VHDL 2008 support, you can use the new package ieee.numerc_std_unsigned, which essentially makes std_logic_vector behave like unsigned. Also, since I didn't see it stated explicitly, an actual code example to convert from an (unsigned) integer to an std_logic_vector: use ieee.numeric_std.all. As LoneTech says, use ieee.numeric_std is your friend. You can convert a std_logic_vector to an integer, but you'll have to cast it as signed or unsigned first (as the compiler has no idea which you mean).

VHDL is a strongly typed language. I've on this subject Fundamentally, I'd change your 7seg converter to take in an integer (or actually a natural, given that it's only going to deal with positive numbers) - the conversion is then a simple array lookup. Set up a constant array with the conversions in and just index into it with the integer you use on the entity as an input. Let's say that your 4-bit counter had an INTEGER output SOME_INTEGER, and you wanted to convert it to a 4-bit STD_LOGIC_VECTOR SOME_VECTOR '0'); end if; EDIT: You shouldn't need to declare the variable as an Integer. Try changing the declaration to std_logic_vector instead. The + and - operators work on std_logic_vectors.

Yaad Aa Raha Hai Remix Mp3 Free Download on this page. Convert binary number to BCD in VHDL or Verilog using the Double Dabble method on an FPGA. Convert Binary numbers to BCD in VHDL and Verilog. Showtek Today Is Tomorrow Rapidshare Downloader. Conversion to Verilog and VHDL — My. 0 documentation. This feature provides a path from My. Standard Verilog or VHDL based.